ecn变更模板Driver的VOL范围全部落入Receiver的VIL窗口之内时ECL PECL LVPECL信号都是什么?它们的优瑕疵和电道图精确认识

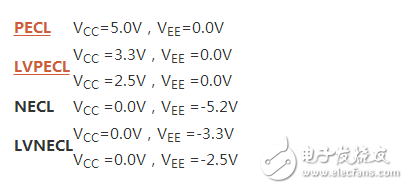

ECL电道(即发射极耦合逻辑电道Emitter-Couple Logic)是一种非饱和型的数字逻辑电道,电道内晶体监工作正在线性区或截止区,速率不受少数载流子的存储工夫的限度,以是它是现有种种逻辑电道中速率最速的一种, 能餍足高达10Gbps任务速度。最先由Motorola公司提出ECL轨范。ECL 的要紧分类如下。

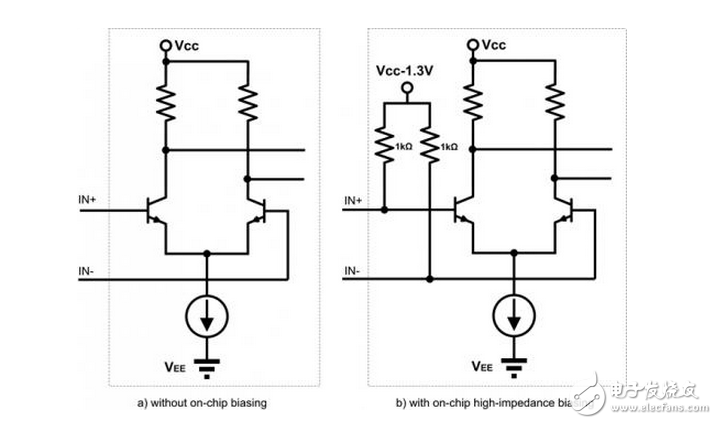

PECL 的输入是一个具有高输入阻抗的差分对,该差分对的共模电压必要偏置到VBB =VCC-1.3V,如许答应的输入信号电平动态最大。闭于差异芯片的输入级,信号答应的共模电平能够会有些分别,请参考相应的datasheet。有个人芯片正在内部一经集成了偏置电道,运用时直接相接即可,有的芯片没有加,运用时必要正在芯片外部加直流偏置。

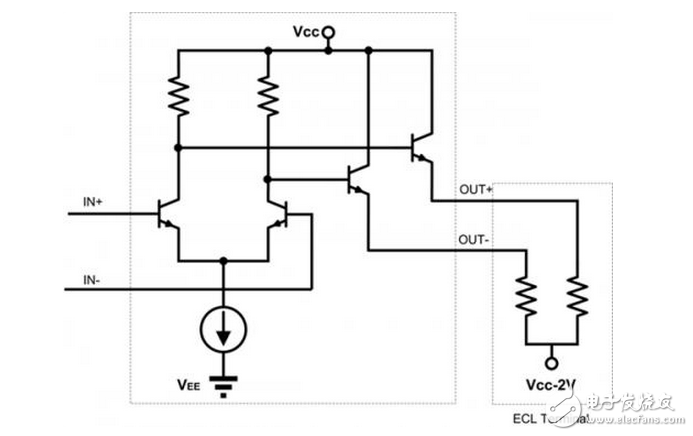

1)扇出本领强。ECL输出阻抗低(6~8ohm),输出阻抗高(平常为10kohm),以是扇出系数很高。

2)噪声低,对电源央求低。ECL/PECL器件对电源电压的同步变革是不太敏锐的,是以能够正在ECL某些行使中相对地松开对电源波纹、误差和分拨的央求。有时答应电道的电源电压范ECL围可宽至10%。因为差分电道两臂瓜代任务,电道任务时电源电流根基上恒定(不随逻辑状况变革而变革,也不随任务频率推广而推广),是以能够推敲放宽对电源内阻的央求。

3)速率速。晶体监工作时不进入饱和状况,只任务正在线性区和截止区,没有少数载流子的存储形象,开闭工夫大为缩短;集电结电容大大减小,RC工夫常数也相应减小,电道的传输延迟工夫就很短;电道的逻辑电平摆幅小(单端小于850mV),正在动态转换流程中各个结上的电压变革对结电容(征求寄生电容)的充放电工夫很短。

1)ECL的瑕疵也很显着,那即是功耗大。能够说,ECL 的高速机能是用高功耗为价格换来的。

ECL逻辑的上下电平之差大凡为800mV,个中心参考电平(共模电压)VBB依照VCC变革,大凡为VCC-1.3V。是以,PECL的电平随VCC的差异而差异。如:

当然,以上的直流性情只是对大凡而言,实质上到整体的器件上仍旧会稍有差异,统一器件的输入和输出也纷歧样。正在安排的岁月,都应当参考相应器件的datasheet来得到其精确的电气特质。

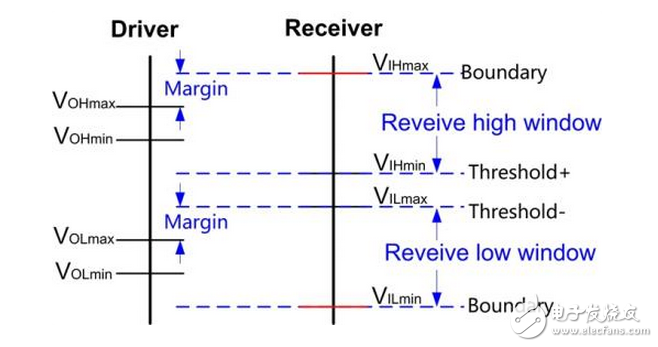

闭于直流性情,另有很紧要的一点即是两个ECL器件之间的接口配合,也即是说,咱们要卓殊闭心Driver的输出是否正在Receiver的输入的容差边界之内。咱们称这个容差边界为“给与窗口”。假使Driver的输出没有落正在这个给与窗口之内,就有能够形成给与端的误判,从而形成安排上的让步。

是以看两个ECL器件是否可能互连,闭于Driver,只若是从DATASHEET中获得其输出高电平VOH和输出低电平的VOL的边界;闭于Receiver,只须看其闭于给与窗口的极少目标,分两种情状。

假使ECL用作单端信号的话(这种情状并不众睹),互连理解顺利腕与LVTTTL,COMS等单端信号的手腕相像。

必要闭心的是输入高电平VIH和输入低电平VIL的最大和最小值,VIH的最大和最小值组成了VIH的给与窗口,VIL的最大和最小值组成了VIL的给与窗口。如下图:

当Driver的VOH边界统共落入Receiver的VIH窗口之内,Driver的VOL边界统共落入Receiver的VIL窗口之内时,能够保障Receiver能够精确给与Driver的输出,不然会有潜正在的互连不精确以至损坏器件的能够。

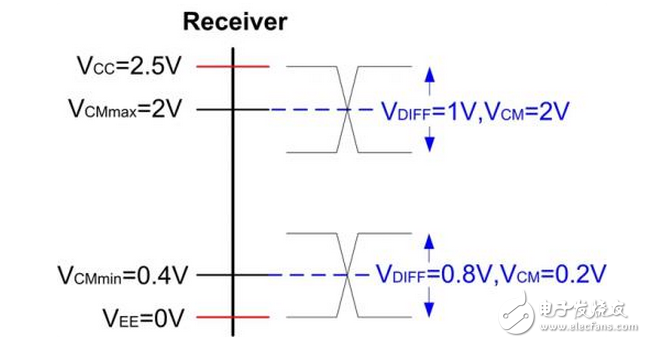

闭于差分信号,要闭心的目标是输入共模电平VCM和差分信号VDIFF边界。

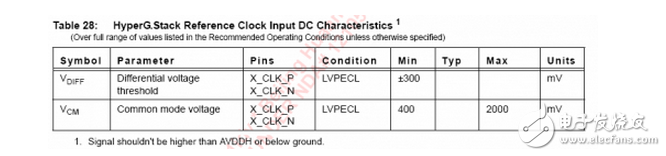

如某器件的某输入口任务正在LVPECL形式下。其目标如下(AVDDH=2.5V):

那么其给与窗口如下图所示,图中标出了共模电压为最大或者最小时,其答应的最大单端电压。

餍足以上条款的差分信号都能够被精确给与。能够提防到,假使共模信号被端接到VBB =VCC-1.3V,担当窗口最大。

由上可睹,差分信号有比单端信号宽得众的给与窗口,这也是高速行使中差分信号被集体采用的起因之一。

转载请注明出处:MT4平台下载

本文标题网址:ecn变更模板Driver的VOL范围全部落入Receiver的VIL窗口之内时