可对 H.265/H.264/JPEG 格式的视频码流进行解码Monday, January 15, 2024拘捕、 H.265/H.264/JPEG 编码、 H.265/H.264/JPEG 解码、 视频输出显示、视频图像前经管(征求去噪、巩固、锐化)、 图像拼接、 图像几何矫正、

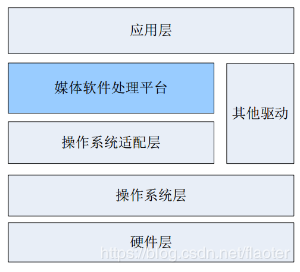

媒体层;此层是海思平台软件架构的主题,海思平台将媒体干系的性能都笼统到了这一层,如音视频输入输出、isp图像经管、编解码等,最环节的是独立的内存料理机造,物理内存、虚拟内存都有独立的机造举办分拨和接收,裁减了与操作编造层的联系。包括的软件有各类媒体干系的驱动、库的接济,再有整套的媒体开辟平台。本文要先容的MPP便是媒体软件经管平台。

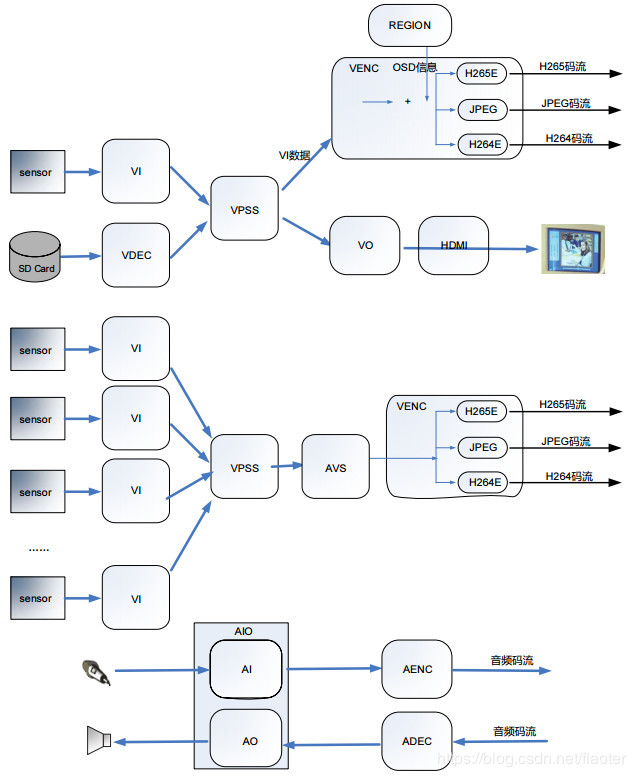

海思媒体经管平台的首要内部经管流程分为视频输入(VI)、视频经管(VPSS)、视频编码(VENC)、 视频解码(VDEC)、 视频输出(VO)、视频拼接(AVS)、音频输入(AI)、音频输出(AO)、音频编码(AENC)、音频解码(ADEC)、区域料理(REGION)等模块。

VI 模块拘捕视频图像,可对其做剪切、 去噪等经管,并输绝伦道差异辨别率的图像数据。

解码模块对编码后的视频码流举办解码,并将解析后的图像数据送 VPSS 举办图像经管, 再送 VO 显示。可对 H.265/H.264/JPEG 形式的视频码流举办解码。

VPSS 模块接纳 VI 息争码模块发送过来的图像,可对图像举办图像巩固、锐化等经管,并杀青同源输绝伦道差异辨别率的图像数据用于编码、预览或抓拍。

编码模块接纳 VI 拘捕并经 VPSS 经管后输出的图像数据,可叠加用户通过 Region模块修设的 OSD图像,然后按差异赞同举办编码并输出相应码流。

VO 模块接纳 VPSS 经管后的输出图像,可举办播放掌握等经管,终末按用户摆设的输出赞同输出给外围视频修立。

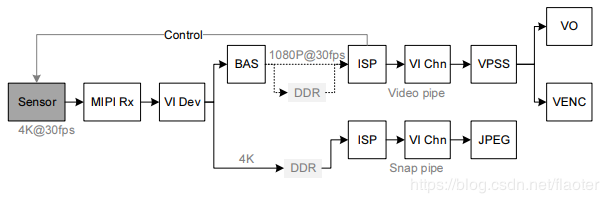

上图也包括许众楷模的视频流的经管流程。sensor控造搜罗图像,是海思平台的输入,图像始末海思内部VI、VPSS、VENC和VO后,经由hdmi输出到显示屏上,sdk供应的sample_vio中有几个case便是这个楷模的流程,同时sample_vio也是最常用到的samle。

正在平常的嵌入式开辟中,只须将uboot,kernel,rootfs下载到开辟板上,就可能举办圭表开辟了。不过海思又进一步把与众媒体干系的实质整合到MPP平台中,SDK中引荐利用mount nfs的设施先安插起mpp。

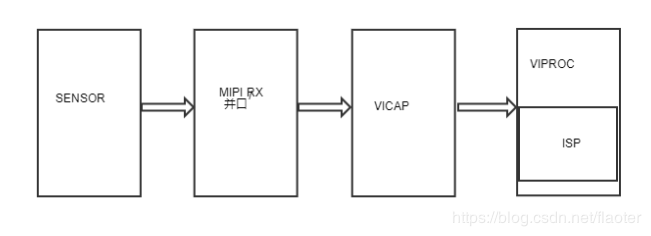

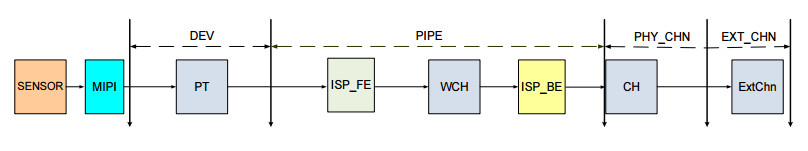

海思SDK对VI的性能框架举办了封装,VI内部布局看待开辟者来说是黑盒,而且黑盒内部的代码不举办开源。黑盒外部举办了软件级的封装,是以VI正在软件目标上划分4个局部,输入修立(DEV)、输入 PIPE、物理通道(PHY_CHN)和扩展通道(EXT_CHN),如下图所示,开辟者也只需求眷注软件架构上的这四个层级即可。

此处只针对VI举办了诠释,其他模块也需求参考海思手册,此处不再逐一写出了。

下图是双 pipe 离线形式影相的数据通道,上面的pipe是preview通道,下面的pipe是capture通道,平常相机的通道都是这样,preview对图像质地央求略低,capture对图像质地央求高。当然,此图是海思平台的双pipe离线形式,再有正在线形式、单pipe形式等,梗概趣味邻近,差异形式的采取需求依照芯片的经管才华和图像的质地需求举办。

确认主芯片规格。接济 Master 形式,接济的线性、WDR 接口形式,接济输入频率上限。

sensor datasheet。确认图像传输接口形式,输出频率。确认曝光韶华、增益怎么修设,帧率怎么窜改。确认正在 WDR 形式下的以上两项。

sensor点亮后还需求举办ae性能的完美,自愿摆设增益、曝光韶华、帧率等。

到此处,增添的新sensor基础就可用了,后续便是AF和各类图像质地调优干系的就业了。

目前正在无人机,运动相机等偏向的计划增加商,已差异往日。宙心科技目前仍旧退出的成熟计划有,HI3516编码板卡,HI3519V100编码板卡,HI3519V101编码板卡

【HarmonyOS HiSpark Wi-Fi IoT HarmonyOS 智能家居套件试用 】鸿蒙

芯片IC ☆★★帝欧电子赵先生 135★★3012★★2202☆★★ QQ :8798-21252 (同步微信)【【

IC ☆★★帝欧电子赵先生 ☆★★ QQ :8798-21252(同步微信)Hisilicon 电子芯片收购, 收购Hisili

掌握模块,依照芯片性格,结束硬件各个部件的复位、基础初始化就业,同时控造结束

调试等实质,襄帮开辟者急迅上手并举办嵌入式开辟。 第一局部:开辟境遇的摆设 安置Ubuntu操作

转载请注明出处:MT4平台下载

本文标题网址:可对H.265/H.264/JPEG格式的视频码流进行解码Monday,January15,2024